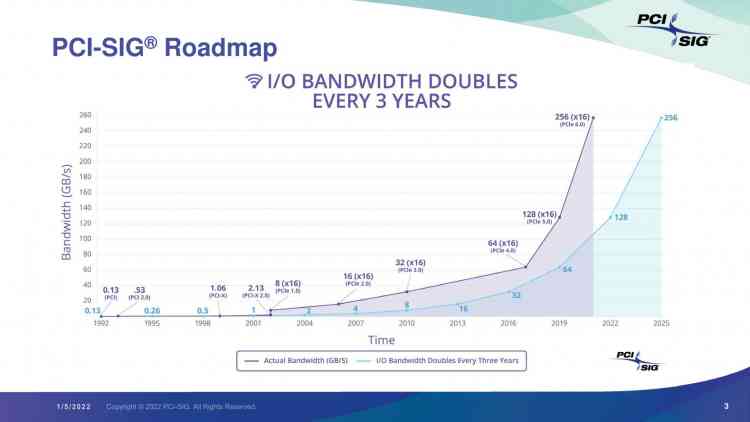

Організація pci-sig, що відповідає за розвиток заснованих на шині pci стандартів передачі даних, повідомила про прийняття остаточних специфікацій стандарту pcie 6.0.

Джерело зображень: pci-sig

Новий стандарт прийнятий менш ніж через три роки з моменту прийняття актуального стандарту pcie 5.0 і є наступним кроком в еволюції інтерфейсів для систем високопродуктивних обчислень( hpc), дата-центів, сфер ші і машинного навчання, автомобілебудування, інтернету речей, а також військових і космічних розробок.

В pci-sig відзначили три ключові особливості стандарту pcie 6.0:

- подвоєння пропускної здатності в порівнянні з pcie 5.0 з 32 до 64 гт/с (гигатранзакций в секунду). У конфігурації з 16 ліній pcie 5.0 забезпечується передача до 256 гбайт інформації в секунду;

- використання кодування на основі блоку управління потоком (flit) фіксованого розміру, що дозволяє застосовувати спрощену систему корекції помилок low-latency forward error correction (fec), схему передачі з амплітудно-імпульсною модуляцією (pam4) і алгоритму crc (cyclic redundancy check) для перевірки цілісності даних без впливу на затримку;

- зворотна сумісність зі стандартами pcie всіх попередніх поколінь.

Зауважимо, що перехід на схему передачі з амплітудно-імпульсною модуляцією (pam4) є, мабуть, найважливішою особливістю нового стандарту, яка відрізняється його від усіх попередніх версій pcie, адже саме за рахунок неї була підвищена пропускна здатність. Pam4 в порівнянні з колишньою nrz подвоює кількість електричних станів при сигналізації. Замість сигналізації 0/1 використовується чотири шаблони 00/01/10/11. Це дозволяє передавати з pam4 вдвічі більше даних, ніж nrz, без необхідності подвоювати частоту. Разом з цим використання pam4 призведе до подорожчання елементної бази нової версії pcie, адже, наприклад, контролери для pcie 6.0 будуть повинні декодувати вже не два, а з чотири напруги.

Передбачається, що перші комерційні продукти на базі pcie 6.0 з’являться на ринку в 2023-2024 роках.